CMOS邏輯電路實現(xiàn)

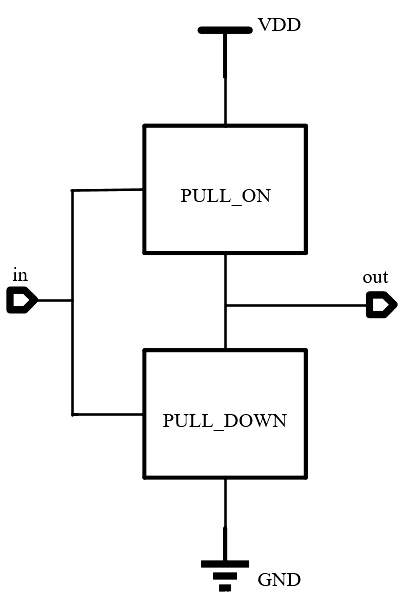

CMOS邏輯電路,分兩部分,上拉部分,下拉部分。上拉部分由PMOS管電路構(gòu)成,下拉部分由NMOS管電路組成,如下。上下拉,形成互補。

由前面的基礎(chǔ)可知,CMOS只能實現(xiàn)基本邏輯的非,比如或邏輯,與邏輯,如果不加反相器,CMOS只能實現(xiàn)或非,與非邏輯。原因就是上拉邏輯只能用PMOS實現(xiàn),下拉邏輯只能由NMOS實現(xiàn),而PMOS的導(dǎo)通需要輸入信號為0,NMOS導(dǎo)通需要輸入信號為1。

一般的設(shè)計過程

既然如此,在用CMOS實現(xiàn)邏輯電路時,一般可以照如下順序去做:

可以先將其整體先加上一個非,作相應(yīng)的邏輯轉(zhuǎn)化。

上拉邏輯中各個PMOS,與操作為并聯(lián),或操作為串聯(lián)。

下拉邏輯中各個NMOS,與操作為串聯(lián),或操作為并聯(lián)。

舉例說明

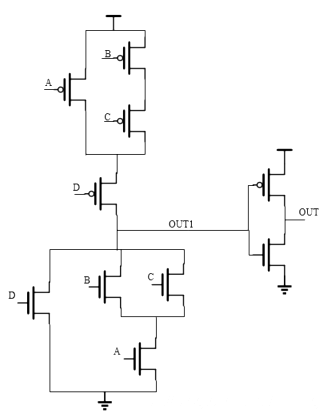

比如我們想從CMOS層去實現(xiàn)邏輯 OUT = D+A*(B+C) (減號“-”表示取反(非)操作,“+”表示或,*表示與)。

設(shè)計過程如下:

OUT = - ( -(D+A*(B+C)) )

OUT1 = -(D+A*(B+C))

OUT = -OUT1

對于OUT1 = -(D+A*(B+C)),正好是邏輯整體上帶了個非,設(shè)計(D+A*(B+C))部分之后再加上一個非即可。

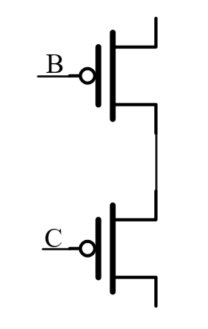

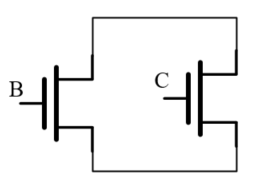

故對于上拉邏輯:

1.或操作為串聯(lián),從而輸入B,C接到的PMOS之間為串聯(lián)。

2.與操作為并聯(lián),故輸入A接到的PMOS跟B,C或邏輯之間為并聯(lián)。

3.或操作為串聯(lián),故D與A*(B+C)的PMOS邏輯為串聯(lián)。

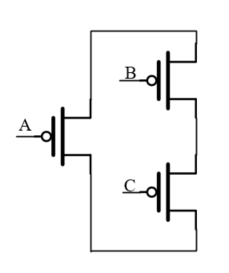

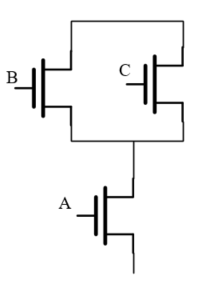

對于下拉邏輯與上拉邏輯正好相反:

4.或操作為并聯(lián),從而輸入B,C接到的NMOS之間為并聯(lián)。

5.與操作為串聯(lián),故輸入A接到的NMOS跟B,C或邏輯之間為串聯(lián)。

6.或操作為并聯(lián),故D與A*(B+C)的NMOS邏輯為并聯(lián)。

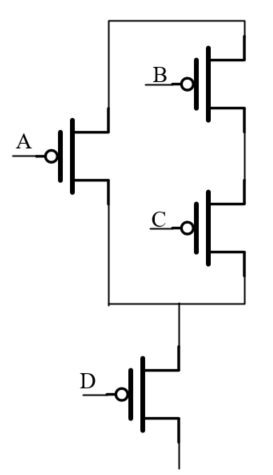

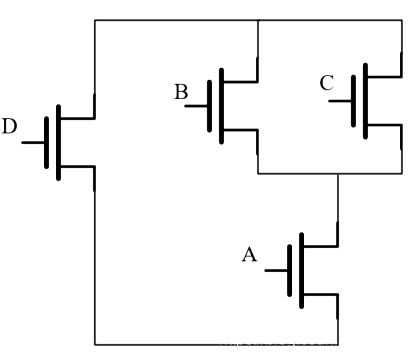

7.從而得到 OUT1 = -(D+A*(B+C)) 的CMOS實現(xiàn)如下:

過程中上下拉兩部分的邏輯式相同,組合起來后,自行補充一個非。

則實際分析電路中,一般只需單獨分析一部分就行了。

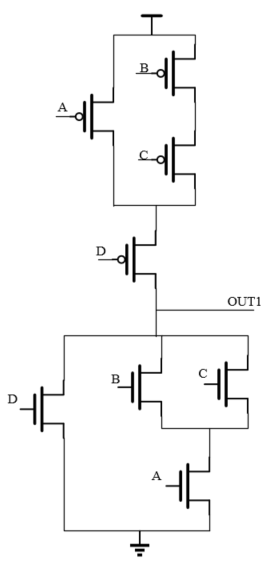

8.OUT = -OUT1,故得最終答案如下:

當(dāng)然,在MOS管級別還可以做一些優(yōu)化,比如MOS管級別的邏輯優(yōu)化,MOS管柵源共用,晶體管尺寸調(diào)整,重新安排各個輸入的上下順序等等,都可以在MOS管級別使得電路的時序與面積功耗等得到優(yōu)化,但這不是我們的重點,一般對于全定制IC設(shè)計會從MOS管級開始考慮電路的實現(xiàn)。這里只是對其做一個了解。

實際設(shè)計的重點還是會注重于門級以上的電路實現(xiàn)與優(yōu)化,特別是到了Verilog描述,主要著重于數(shù)據(jù)流級,行為級描述。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280